Abstract

The multilevel current states of synaptic devices in artificial neural networks enable next-generation computing to perform cognitive functions in an energy-efficient manner. Moreover, considering large-scale synaptic arrays, multiple states programmed in a low-current regime may be required to achieve low energy consumption, as demonstrated by simple numerical calculations. Thus, we propose a three-terminal Cu-ion-actuated CuOx/HfOx/WO3 synaptic transistor array that exhibits analogously modulated channel current states in the range of tens of nanoamperes, enabled by WO3 channel engineering. The introduction of an amorphous stoichiometric WO3 channel formed by reactive sputtering with O gas significantly lowered the channel current but left it almost unchanged with respect to consecutive gate voltage pulses. An additional annealing process at 450 °C crystallized the WO3, allowing analog switching in the range of tens of nanoamperes. The incorporation of N gas during annealing induced a highly conductive channel, making the channel current modulation negligible as a function of the gate pulse. Using this optimized gate stack, Poole–Frenkel conduction was identified as a major transport characteristic in a temperature-dependent study. In addition, we found that the channel current modulation is a function of the gate current response, which is related to the degree of progressive movement of the Cu ions. Finally, the synaptic characteristics were updated using fully parallel programming and demonstrated in a 7 × 7 array. Using the CuOx/HfOx/WO3 synaptic transistors as weight elements in multilayer neural networks, we achieved a 90% recognition accuracy on the Fashion-MNIST dataset.

Similar content being viewed by others

Introduction

In this era of big data, the amount of data to be processed has increased significantly. Data processing through the conventional von Neumann computing architecture, where the processor and memory units are physically separated, has caused significant latency bottlenecks and power consumption1. To address this challenge, brain-inspired neuromorphic systems using parallel-connected biological synapses have been proposed as new computing architectures to enhance computation efficiency2,3,4,5. To implement this architecture in hardware systems, it is important to emulate the functions of biological synapses using analog memory devices. Among the various candidates for synaptic devices, resistive switching random-access memory (RRAM) has mainly been explored because of its scalability6,7,8. The multiple resistance states of RRAM can be demonstrated by the precise control of the formation and rupture of local conductive filaments through materials engineering and novel programming schemes9. However, stochastic ion motion in the switching layer interferes with the filament, causing a nonuniform synaptic response with respect to the programming pulses10,11,12,13,14.

For uniform analog synaptic devices, ion-actuated transistors, which have also been referred to as electrochemical random-access memory or redox transistors and were inspired by the field-driven Li ion motion of rechargeable batteries, have recently been suggested15. Instead of the gate dielectric of a conventional transistor, an electrolyte that not only contains mobile ion sources but also allows ionic motion driven by the field can be utilized. As the number of ions attracted (or repulsed) to the channel layer increases (or decreases), the channel current (ID) between the source (S) and drain (D) is gradually tuned towards higher (or lower) levels as a function of the positive (or negative) programing pulses applied to the gate (G). Thus far, this analog switching behavior has been demonstrated in synaptic transistor unit cells for various combinations of electrolyte/channel material stacks and mobile ion species such as Li, H, O, and Cu ions15,16,17,18. Recent advances in synaptic transistors have been extended to array-level analyses19,20,21. Analog switching of some or all cells in arrays that can be updated simultaneously has been experimentally achieved using a half-bias scheme, where the drain voltage (VD) and gate voltage (VG) are used during programming. It is worth noting that the ID of the synaptic transistor should be as low as possible considering the energy consumption at the array level21. This is because, unlike usual transistors serving as switch elements, analog synaptic transistors are always on-channel without a threshold voltage required to allow current to flow in the channel. The magnitude of the ID of the synaptic transistor is tuned only by the VG. Assuming that only the farthest synaptic transistor in the array is programmed, unselected synaptic transistors located on a horizontal (or vertical) line applied to VG (or VD) generate unwanted gate (or drain) leakage currents, as shown in Fig. 1a. In particular, although extremely low gate currents (IGs) of several tens of picoamperes have been reported to date, the ID has mainly been several microamperes15,16,17,18,22. This implies that the magnitude of the ID is primarily related to the energy consumption in the synaptic array and its impact becomes significant as the array size increases, as shown in Fig. 1b.

(a) Schematic illustration of leakage current sources in synaptic arrays. The half-bias scheme was used to program the farthest cell for simplicity. (b) Numerical calculations show the impact of leakage currents on energy consumption with respect to array size. Energy was calculated considering the leakage currents originated from unselected synaptic transistors, where either VG or VD was applied.

Therefore, we fabricated a CuOx/HfOx/WOx synaptic transistor array that exhibited analog switching in the range of tens of microamperes. Next, the effect of the WOx channel layer was investigated using the sputtering method and annealing conditions related to the stoichiometry and crystallinity of the material.

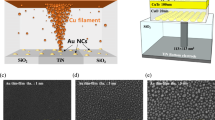

The Cu-ion-actuated synaptic transistor structure developed in our previous study was used in this study18. For the synaptic transistor array, S and D lines consisting of W were patterned on an Si/SiO2 wafer, as shown in Fig. 2a. Via-holes for the S/D contacts were defined after Si3N4 interlayer deposition. A WOx channel with a length (or width) of 20 (or 5) μm was deposited by sputtering with a WO3 single target. For comparison, a different channel layer was formed by reactive sputtering with a W metal target under ambient Ar and O plasma conditions. Additional annealing was performed at 450 °C using a rapid thermal annealing system to lower ID in the range of nanoamperes. Subsequently, an HfOx electrolyte and CuOx G with a length of 10 μm were deposited by sputtering using HfOx and Cu targets, respectively. Finally, a W capping layer was formed on top of the G and S/D contacts by sputtering. The thickness of each layer was evaluated by alpha step at the 3-D convergence center of Inha University. The fabricated CuOx/HfOx/WOx synaptic transistor was analyzed using transmission electron microscopy (TEM) and X-ray photoelectron spectroscopy (XPS) depth profiling, and each layer was clearly distinguished, as shown in Fig. 2b and c.

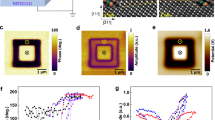

The electrical characteristics of the CuOx/HfOx/WOx unit synaptic transistor were evaluated by applying a VG of + 6 V (or − 5 V) with a pulse width of 100 ms to increase (or decrease) the ID, as shown in Fig. 3a. The tuned ID was sensed by applying a VD of 0.5 V. The observed switching behavior was attributed to the reversible driving of Cu ions back and forth through the HfOx layer. The effective thickness of HfOx was thinned or thickened, and the electric field-adjusted channel conductivity was enhanced or weakened23. As reported in a previous study, a limited number of Cu ions was provided by the CuOx G electrode, which could be effectively and precisely controlled by successive VG pulses to allow linear and symmetric synaptic behavior in the range of tens of microamperes18. Under the given programming conditions, we first analyzed the effect of the stoichiometry of the channel layer. A stoichiometric WO3 layer was formed by reactive sputtering with O gas injection, as shown in Fig. 3b. Although an extremely low ID at a level below tens of picoamperes was measured, no change in ID was observed as a function of VG pulses. When annealing was conducted at 450 °C and atmospheric pressure for 30 min, ID became higher and began to be analogously controlled by the VG pulses, as shown in Fig. 3c. The WO3 layer crystallizes at temperatures above 400 °C24. The polycrystalline WO3 layer, which was verified by the fast Fourier transform in the TEM analysis (inset of Fig. 3c), boosted the conductivity. Thus, most of the applied VG was transferred to the HfOx electrolyte to drive the Cu ions, leading to a progressive increase and decrease in ID for 200 consecutive VG pulses. However, when ambient N gas was applied during annealing, ID was increased to hundreds of microamperes, making the ID modulation negligible, as shown in Fig. 3d. To identify the impact of the annealing gas on analog switching, the W 4f peak at the WO3 channel interface of the two annealed devices, obtained through XPS analysis, was investigated, as shown in Fig. 3e. Two peaks at binding energies of approximately 31 and 34 eV, indicating metallic states related to nonstoichiometric WOx were clearly observed for both samples. However, two peaks corresponding to WO3 observed at 36.5 and 38 eV were noticeable for the annealed sample without N gas. This implies that N preferentially bonds to W. W–N bonding is usually represented by metallic peaks (approximately 31 and 34 eV); therefore, the enhanced channel conductivity can be attributed to the conductive WN formed.

VG of + 6 V (or − 5 V) with a pulse width of 100 ms was used for all devices to evaluate device characteristics. (a) Analog synaptic behavior observed in the synaptic transistor employing amorphous WOx channel. (b) No switching was observed when relatively stoichiometric WO3 channel was used. (c) Crystallized WO3 channel, which was verified by fast Fourier transformation image, allowed the ID to be adjusted by pulse number. (d) Increased ID level due to N annealing hid the switching behavior. (e) W 4f peak obtained through XPS analysis.

Next, we studied the temperature dependence of the IG to identify the mechanisms of analog switching in the optimized gate stack. IG, which was obtained by applying voltage to G and grounding S, was measured by raising the temperature to 140 °C. As a result, the transport characteristics were suitably fitted using the Poole–Frenkel emission, as shown in Fig. 4a. This indicates that bulk switching across the entire electrolyte area was involved, rather than metallic conduction, owing to the locally clustered Cu ions. Specifically, by comparing simultaneously obtained IG and ID, we found that the IG response to VG pulses was related to ID modulation, as shown in Fig. 4b. That is, the gradual transition of IG by a single VG pulse during initial programming was typically projected onto the lateral ID, resulting in a linear ID response in working cell. However, at the given programming condition, nonlinear ID behavior was often observed in non-optimized stacks. When we examined the IG response of these failed cells, the abrupt increase and saturation of IG was observed. These results imply that the extent to which Cu ions move steadily through the electrolyte per VG pulse is related to the linearity and symmetry of ID.

Finally, we evaluated synaptic arrays employing the engineered WO3 channel. As the channel resistance was reduced, a larger electric field across the HfOx layer was used to drive the Cu ions; therefore, analog switching could be achieved by lowering VG to + 3 V. To facilitate fully parallel programming, all the G, S, and D pads of the 7 × 7 array were contacted by a probe card, as shown in Fig. 5a. In the half-bias scheme, the + 3 V (or − 3 V) required to program the unit cell was halved, and + 1.5 V (or − 1.5 V) was simultaneously applied to VG and VD. Consequently, a full voltage of approximately ± 3 V was applied to the selected cells. Reliable analog switching behavior was obtained for all synaptic transistors. The cell-to-cell update curves expressed as the median repeatedly increase and decrease, as the polarity of the pulse changes every 50 times for a total of 200 pulses, as shown in Fig. 5b. Specifically, the ID states updated by the first 50 potentiation pulses reached its maximum value and returned to the initial state by the next 50 depression pulses. As a result, the ID states applied at the first, 100th, and 200th pulses (or 50th and 150th) showed uniform cycle-to-cycle distribution, as shown in Fig. 5c. Note that although the reversible analog ID modulation from all cells was achieved, cell-to-cell uniformity in the array needed to be improved. We recently revealed that the effect of Cu ion distribution (or concentration) in the stack on the synaptic behavior through physics-based simulation25. Based on the clue, further study is currently underway on process development and strategies to ensure reliability as well as uniformity by controlling the adequate amount of Cu ions in the device.

(a) Optical microscope image of fabricated synaptic transistor array contacted by probe card. To update all synaptic transistor cells simultaneously, 50 VG (or VD) pulses of + 1.5 V (or − 1.5 V) were consecutively addressed to all G (or D) lines to increase ID. By changing the polarity of each pulse, ID can be steadily lowered. (b) Reliable synaptic behaviors expressed as median were obtained from all cells. (c) Distributions of IDs when pulses were applied every 50 cycles from the initial state. (d) Pattern recognition accuracy of multilayer perceptron evaluated using IBM analog hardware acceleration kit simulator. The parameters used in this simulation were listed in the table.

Based on these results, we built multilayer neural networks with size 784-256-128-10 (from input to output neurons) designed for image recognition, as shown in Fig. 5d. The input signals were transferred from input neurons to output neurons through synaptic weights, which served as the optimized synaptic transistor in this study. The degree of linearity of synaptic characteristics is expressed by a linearity factor, α, which is calculated by the following equation:26

where, GMAX and GMIN are conductance at the maximum and minimum ID state, respectively, and \(\omega\) is an internal variable which ranges from 0 to 1. Moreover, α is equal to 1 in the case of the ideal synaptic behavior. Based on these equations, linearity of potentiation (or depression) of 1.47 (or − 1.61) was achieved for the developed synaptic transistor. The difference between the maximum and minimum ID states of ~ 4 was also used in the simulations. Subsequently, the recognition accuracy on the Fashion-MNIST dataset was evaluated with a learning rate of 0.01 using the IBM analog hardware acceleration kit simulator by assuming that the achieved synaptic transistors served as weight elements26. Consequently, our device exhibited a recognition accuracy of approximately 90%, which is comparable to the baseline, when the multilevel states were almost linearly adjusted15,27.

Finally, through simple numerical analysis, we showed that update energy consumption is reduced by lowering ID of the synaptic transistors, which are assumed to be configured in 1 K array, as shown in Fig. 6. Compared to reported synaptic transistors that utilize the Li or O ions, the VG to drive the Cu ions seemed to be larger. Current has a greater impact on power than voltage because its magnitude can be changed significantly. To date, the energy consumed to change the ID state by a single VG pulse has been mainly discussed considering unit cell operation28. However, to sequentially update all cells in the array, the VG and VD signals were applied to the array via all interconnect lines. Thus, synaptic transistors with tunable ID in the low current regime enable low-power operation because the ID is typically higher than the IG. In addition to energy consumption, recent study showed that recognition accuracy is degraded due to interference from high IDs of neighboring cells29. These results mean that the range of ID, which has often been ignored, should be considered when designing a three-terminal synaptic transistor.

In this work, we achieved analog switching in a low ID regime (< 100 nA) of a 7 × 7 CuOx/HfOx/WO3 synaptic transistor array using WO3 channel engineering. Specifically, we revealed that the ID range could be lowered or increased by utilizing a stoichiometric WO3 layer or by strengthening the crystallinity. In addition, the steady and gradual motion of the Cu ions across the gate stack enabled a linearly tuned ID response. The obtained synaptic behavior not only accurately inferred the Fashion-MNIST dataset but also performed recognition with low energy consumption.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323 (2019).

LeCun, Y., Bengio, Y. & Hinton, G. Deep learning. Nature 521, 436–444 (2015).

Mead, C. Neuromorphic electronic systems. Proc. IEEE 78(10), 1629–1636 (1990).

Esser, S. K. et al. Convolutional networks for fast, energy-efficient neuromorphic computing. PNAS 113(41), 11441–11446 (2016).

Tang, J. et al. Bridging biological and artificial neural networks with emerging neuromorphic devices: Fundamentals, progress, and challenges. Adv. Mater. 31, 1902761 (2019).

Burr, G. W. et al. Neuromorphic computing using non-volatile memory. Adv. Phys.: X 2(1), 89–124 (2017).

Boybat, I. et al. Neuromorphic computing with multi-memristive synapses. Nat. Commun. 9, 2514 (2018).

Ielmini, D. & Ambrogio, S. Emerging neuromorphic devices. Nanotechnology 31, 092001 (2019).

Woo, J. et al. Improved synaptic behavior under identical pulses using AlOx/HfO2 bilayer RRAM array for neuromorphic systems. IEEE Trans. Electron Dev. 63(12), 5064–5067 (2016).

Wu, W. et al. Improving analog switching in HfOx-based resistive memory with a thermal enhanced layer. IEEE Electron Dev. Lett. 38(8), 1019–1022 (2017).

Choi, S. et al. SiGe epitaxial memory for neuromorphic computing with reproducible high performance based on engineered dislocations. Nat. Mater. 17, 335–340 (2018).

Woo, J. et al. Optimized programming scheme enabling linear potentiation in filamentary HfO2 RRAM synapse for neuromorphic systems. IEEE Electron Dev. Lett. 37(8), 994–997 (2016).

Jeong, Y., Kim, S. & Lu, W. D. Utilizing multiple state variables to improve the dynamic range of analog switching in a memristor. Appl. Phys. Lett. 107, 173105 (2015).

Zhao, M., Gao, B., Tang, J., Qian, H. & Wu, H. Reliability of analog resistive switching memory for neuromorphic computing. Appl. Phys. Rev. 7, 011301 (2020).

Tang, J. et al. ECRAM as scalable synaptic cell for high-speed, low-power neuromorphic computing. In 2018 IEEE International Electron Devices Meeting (IEDM) 13.1.1–13.1.4 (2018).

Liu, L. et al. Proton-assisted redox-based three-terminal memristor for synaptic device applications. Appl. Mater. 15(24), 29287–29296 (2023).

Kim, S. et al. Metal-oxide based, CMOS-compatible ECRAM for deep learning accelerator. In 2019 IEEE International Electron Devices Meeting (IEDM) 35.7.1–35.7.4 (2019).

Kang, H., Kim, H. W., Hong, E. R. & Woo, J. Analog synaptic behavior of mobile ion source-limited electrochemical RAM using CuOx oxide electrode for deep learning accelerator. Appl. Phys. Lett. 120, 122101 (2022).

Li, Y. et al. In situ parallel training of analog neural network using electrochemical random-access memory. Front. Neurosci. 15, 636127 (2021).

Lee, C., Kwak, M., Choi, W., Kim, S. & Hwang, H. Improved on-chip training efficiency at elevated temperature and excellent inference accuracy with retention (> 108 s) of Pr0.7Ca0.3MnO3−x ECRAM synapse device for hardware neural network. In 2021 IEEE International Electron Devices Meeting (IEDM) 12.3.1–12.3.4 (2021).

Kang, H. et al. Analysis of electro-chemical RAM synaptic array for energy-efficient weight update. Front. Nanotechnol. 4, 1034357 (2022).

Kang, H. & Woo, J. Cu-ion-actuated three-terminal neuromorphic synaptic devices based on binary metal-oxide electrolyte and channel. Appl. Phys. Lett. 119, 072103 (2021).

Kim, N., Kang, H., Kim, H. W., Hong, E. & Woo, J. Understanding synaptic characteristics of nonvolatile analog redox transistor based on mobile ion-modulated-electrolyte thickness model for neuromorphic applications. Appl. Phys. Lett. 121, 072105 (2022).

Woo, J. et al. Introduction of WO3 layer in a Cu-based Al2O3 conductive bridge RAM system for robust cycling and large memory window. IEEE J. Electron Dev. Soc. 4(3), 163–166 (2016).

Tessler, N., Kim, N., Kang, H. & Woo, J. Switching mechanisms of CMOS-compatible ECRAM transistors-electrolyte charging and ion plating. J. Appl. Phys. 134, 7 (2023).

Rasch, M. J. et al. A flexible and fast PyTorch toolkit for simulating training and inference on analog crossbar arrays. In 2021 IEEE 3rd International Conference on Artificial Intelligence Circuits and Systems (AICAS) 1–4 (2021).

Gong, N. et al. Signal and noise extraction from analog memory elements for neuromorphic computing. Nat. Commun. 9, 2102 (2018).

Lee, J., Nikam, R. D., Kim, D. & Hwang, H. Highly scalable (30 nm) and ultra-low energy (~5fJ/pulse) vertical sensing ECRAM with ideal synaptic characteristics using ion-permeable graphene electrodes. In 2022 IEEE International Electron Devices Meeting (IEDM) (2022).

Kim, S., Son, J., Kwak, H. & Kim, S. Accurate weight update in an electrochemical random-access memory based cross-point array using channel-high half-bias scheme for deep learning accelerator. Adv. Electron. Mater. 2023, 2300476 (2023).

Acknowledgements

This research was supported by the National R&D Program through the National Research Foundation of Korea (NRF), funded by the Ministry of Science and ICT (RS-2023-00258227), and also supported by the National R&D Program through the NRF funded by Ministry of Science and ICT (2020M3H2A1078045). This research was supported by the MOTIE(Ministry of Trade, Industry & Energy (RS-2023-00236568 & RS-2023-00231956) and KSRC (Korea Semiconductor Research Consortium) (1415187475 & 1415187361) support program for the development of the future semiconductor device.

Author information

Authors and Affiliations

Contributions

S. J., H. K., and H. K. conducted the experiments and characterized the devices. K. N. and S. K. characterized the arrays. S. J., H. K., H. K., K. N., S. K., N. K., H. W. K., E. H., S. K., and J. W. discussed the results. S. K. and J. W. supervised the study. S. J., H. K., S. K. and J. W. wrote the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Jeon, S., Kang, H., Kwak, H. et al. WOx channel engineering of Cu-ion-driven synaptic transistor array for low-power neuromorphic computing. Sci Rep 13, 22111 (2023). https://doi.org/10.1038/s41598-023-49251-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-023-49251-6

- Springer Nature Limited