Abstract

Two-dimensional materials have recently been spotlighted, due to their unique properties in comparison with conventional bulk and thin-film materials. Among those materials, MoS2 is one of the promising candidates for the active layer of electronic devices because it shows high electron mobility and pristine band gap. In this paper, we focus on the evolution of the electrical property of the MoS2 field-effect transistor (FET) as a function of post-annealing temperature. The results indicate that the off current drastically decreased at 200°C and increased at 400°C while other factors, such as the mobility and threshold voltage, show little variation. We consider that the decreasing off current comes from the rearrangement of the MoS2 film and the elimination of the surface residue. Then, the increasing off current was caused by the change of the material's composition and adsorption of H2O and O2.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Background

Two-dimensional (2D) materials, such as graphene and transition metal dichalcogenides (MoS2, MoSe2, WS2, etc.), are widely used recently for fabricating next-generation nanoelectronics [1-10]. This is because of the high electron mobility of 2D materials, compared with the original bulk material. Typically, graphene shows over 5,000 cm2/Vs of electron mobility [11], and this feature is valuable for applications such as sensors [12] and photovoltaic cells [13]. However, graphene has a fundamental disadvantage for electronic devices, which is the lack of an intrinsic band gap. This has resulted in several reports of insufficient on/off current ratio of field-effect transistors (FETs) [14-17].

Though engineering a band gap of graphene can be an answer for this technical issue, it increases the number of fabrication steps [18,19] and reduces the electron mobility of graphene [20]. As an alternative, MoS2 has an intrinsic band gap, which leads to reduced off current. For example, MoS2 FETs have in general recorded an on/off current ratio of 105 ~ 1010 [21-28], and some MoS2 FETs with high-k dielectrics have recorded an electron mobility of 200 cm2/Vs, which is higher than that of band gap-engineered graphene [21].

Many reports have announced that the annealing process is dispensable for improving the electrical property of various FETs using original IV semiconductors [29], oxide semiconductors [30,31], layered semiconductors [32-34], etc. In the case of 4H-SiC included in the original IV, the annealing process created a passivation layer at the interface, and device parameters were improved, such as the electron mobility and subthreshold swing (SS). In the case of InGaZnO included in oxide semiconductors, the annealing process rearranged defects, and all the device parameters improved, such as V th, SS, mobility, hysteresis, and the on/off current ratio. For graphene included in a layered material, the annealing process eliminated the resist residue on the surface and increased conductance.

For MoS2, a few results have been reported from the viewpoint of the post-annealing process [21,23,26]. One paper showed variation in the optical property, by observing the change of the photoluminescence (PL) peak of single-layer MoS2 with respect to post-annealing [35]. Although it did not evaluate the electrical property of FETs, it reported that the annealing process induced structural rearrangement, and this could also affect the electrical properties of MoS2. Another paper investigated the influence of vacuum annealing on MoS2 FET during measurement of the electrical property [22]. It announced a drastic improvement of electrical performance by annealing, especially in the conductance of the device. However, it focused on the electrical characteristics caused by movement of carriers at elevated temperature, which consequently present the thermally activated characteristics of MoS2 FET. Here, we summarize the evolution of the electrical performance of MoS2 FET at room temperature, which is the conventional operating temperature, with various post-annealing temperatures.

Methods

MoS2 flakes were prepared using a scotch-tape micromechanical cleavage technique, from bulk MoS2 crystal (429ML-AB, SPI Supplies, Inc., West Chester, PA, USA), and were transferred to highly doped silicon substrates covered with 300-nm-thick SiO2. Source and drain (S/D) were patterned by photolithography, and 50-nm-thick Ti was deposited by an e-beam evaporator. Then, a conventional lift-off process was accomplished for the patterning of the S/D electrode. The fabricated MoS2 FET was annealed in a nitrogen environment for 2 h at various temperatures. The electrical characteristic was measured under atmospheric pressure at room temperature. Furthermore, the thicknesses of the MoS2 flakes were measured using atomic force microscopy (AFM; XE-100, Park Systems, Suwon, South Korea).

Results and discussion

Figure 1a is a schematic diagram of the MoS2 FET, and Figure 1b is an AFM profile that corresponds to the red line of the MoS2 image from the inset. The thickness of the MoS2 channel measured by AFM was 11 nm. While there has been controversy over whether using a single-layer MoS2 channel is a requirement for getting higher device performance, some papers proved that a multilayer MoS2 channel was also able to attain comparable device performance, such as a high electron mobility over 100 cm2/Vs and a high on/off current ratio of over 106 [23,36]. Therefore, it is thought that the performance of the multilayer MoS2 is sufficient to study the post-annealing effect.

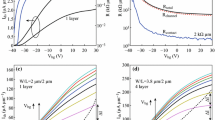

Figure 2 shows the representative I d-V g characteristics under constant V d = 10 V, with respect to the post-annealing temperature among the many multilayer MoS2 FETs shown in Additional file 1: Figure S1. This representative flake has a channel length of 10 μm and a width of 20 μm. This represents the n-type nature of the MoS2 channel that makes the accumulation layer of electrons at positive gate biases, and it is observed as increasing the drain current at positive gate biases. Theoretically, the drain current is supposed to be below 10−9 A at high negative gate biases, due to a depletion layer; however, a drain current of over 10−5 A was observed with various gate biases at room temperature (black line) and at 400°C (pink line). The drain current at the high negative gate biases drastically decreased by approximately 106, compared to that of the device under room temperature, and it seemed that MoS2 has a depletion layer at both 200°C (red line) and 300°C (blue line).

In Figure 3a, the aforementioned transfer curves are arranged in terms of on and off current, with respect to post-annealing temperatures. The on current was defined as the highest drain current measured at high positive gate biases, and the off current was defined as the lowest drain current recorded at low negative gate biases. Figure 3a shows that the on current consistently decreases as the post-annealing temperature increases, while the off current decreases up to 200°C and increases with further increase of temperature. The lowest value of the off current was observed as approximately 10−11 A for the 200°C-annealed device, and this trend is in line with the transfer curve characteristics.

Figure 3b elaborates the field-effect mobility, which increased as the temperature rose and reached a high value of approximately 20.7 cm2/Vs at 200°C and 300°C. The field-effect mobility with respect to the post-annealing temperature is also in accordance with the trend of the off current. Table 1 summarizes the details of the FET device performance parameters as annealing temperature.

Under those trends, the status of the device can be categorized into two regions. The first region, here termed region I, is that in which the device performance improves from room temperature to 200°C with decreasing off current and increasing field-effect mobility. The second region (region II) is that in which the device performance degrades from 200°C to 400°C with increasing off current and decreasing field-effect mobility.

In region I, the decrease of off current is thought to be caused by the atomic arrangement of MoS2 atoms in local sites due to thermal energy. This kind of internal structural modification ends up with the release of a native point defect at the interface between the insulator and the channel material [30]. The interface properties between the MoS2 and SiO2 seemed to be improved, in that the subthreshold swing decreased from 36.20 to 0.91 [V/dec], as the post-annealing temperature increased to 200°C.

Also, it is thought that the resist residue included during the fabrication process might be eliminated by the post-annealing process. The photoresist and organic materials from the 3M tape (3M, St. Paul, MN, USA) are one of the plausible candidates to be eliminated, and specifically, elimination of the photoresist residue of the graphene FET was observed with improvement of the device performance during the post-annealing process [33].

In region II, as mentioned, an increase of the off current by 5 or 6 orders was measured.

First, it is thought that such huge increase is caused by the change of the channel material itself. This is supported by the case of oxide semiconductors, such as InGaZnO4 where desorption of Zn and O atoms over 700°C annealing and degradation in device performance were observed [30]. Similarly, the results of the X-ray photoelectron spectroscopy (XPS) proved that the S to Mo composition ratio significantly increased after annealing at 400°C in N2 (Table 2). Furthermore, time-of-flight secondary ion mass spectroscopy (TOF-SIMS) depth profiles in Additional file 1: Figure S2 show that Mo decreased after annealing at 400°C in N2, which correlated with the XPS data.

From Figure 4, Mo 3d5/2 and S 2p3/2 peaks were shifted in a higher energy by 0.6 and 0.5 eV, respectively, after annealing at 400°C. The molybdenum peak shift means that Mo4+ (228.98 eV) was changed into Mo5+ (230.3 eV) [37], and the S 2p3/2 peak shift toward a high binding energy (over 161.88 eV) has been ascribed to polysulfide or thiomolybdate species [38]. That is, one of the strong candidates for explaining the increase of the off current is the phase transformation of MoS2 into Mo2S5 [39] by thermal energy. Furthermore, previous literature [40] provided evidence for this changed form to have high off current in terms of resistivity.

From a different point of view, adsorption of H2O and O2 on MoS2 can also be one of the reasons for the increase of the off current. Under vacuum conditions, the off current actually decreased by average 102 level and this change is elaborated in Additional file 1: Figure S3. Therefore, it is guessed that adsorption was carried out after the high-temperature annealing process for the measurement of electrical characteristics at an atmosphere environment, and it was also supported by the case of graphene [41].

Conclusions

The evolution of off current for MoS2 FET due to annealing temperature was systematically analyzed. As a result, the off current decreased up to 200°C annealing and increased for higher temperature annealing. Plausible explanations for the decrease in off current are the rearrangement of MoS2 atoms and the elimination of the surface residue. Possible explanations for the increase in off current are the changes of the material's composition ratio and adsorption of H2O and O2. This research is meaningful in that the off current was controlled by the post-annealing temperature.

References

Fengnian X, Damon BF, Yu-ming L, Phaedon A. Graphene field-effect transistors with high on/off current ratio and large transport band gap at room temperature. Nano Lett. 2010;10:715–8.

Thanasis G, Rashid J, Branson DB, Liam B, Roman VG, Sergey VM, et al. Vertical field-effect transistor based on graphene-WS2 heterostructures for flexible and transparent electronics. Nat Nanotechnol. 2013;8:100–3.

Podzorov V, Gershenson ME, Kloc C, Zeis R, Bucher E. High-mobility field-effect transistors based on transition metal dichalcogenides. Appl Phys Lett. 2004;84:3301–3.

Stefano L, Babk F, Emanuel T. Field-effect transistors and intrinsic mobility in ultra-thin MoSe2 layers. Appl Phys Lett. 2012;101:223104.

Steven C, Corsin B, Angelica A, Stephen M, Jeong Seuk K, Xingtian Y, et al. MoS2 P-type transistors and diodes enabled by high work function MoOx contacts. Nano Lett. 2014;14:1337–42.

Song HS, Li SL, Gao L, Xu Y, Ueno K, Tang J, et al. High-performance top-gated monolayer SnS2 field-effect transistors and their integrated logic circuits. Nanoscale. 2013;5:9666–70.

Debtanu D, John M, Sean S, Vincent Z, Arnold G, Haibing P. High on/off ratio field effect transistors based on exfoliated crystalline SnS2 nano-membranes. Nanotechnology. 2013;24:025202.

Fucai L, Hidekazu S, Hui S, Thangavel K, Viktor Z, Neil D, et al. High-sensitivity photodetectors based on multilayer GaTe flakes. ACS Nano. 2014;8:752–60.

Roi L, Ora B, Gregory L, Reshef T, Ernesto J. Field-effect transistors based on WS2 nanotubes with high current-carrying capacity. Nano Lett. 2013;13:3736–41.

Hui F, Steven C, Ting CC, Kuniharu T, Toshitake T, Ali J. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 2012;12:3788–92.

Geim AK, Novoselov KS. The rise of graphene. Nat Mater. 2007;3:183–91.

Schedin F, Geim AK, Morozov SV, Hill EW, Blake P, Katsnelson MI, et al. Detection of individual gas molecules adsorbed on graphene. Nat Mater. 2007;6:652–5.

Xinming L, Hongwei Z, Kunlin W, Anyuan C, Jinquan W, Chunyan L, et al. Graphene‐on‐silicon Schottky junction solar cells. Adv Mater. 2010;22:2743–8.

Damon BF, Yu-Ming L, Phaedon A. Graphene field-effect transistors with self-aligned gates. Appl Phys Lett. 2010;97:013103.

Moon JS, Curtis D, Bui S, Hu M, Gaskill DK, Tedesco JL, et al. Top-gated epitaxial graphene FETs on Si-face SiC wafers with a peak transconductance of 600 mS/mm. IEEE Electr Device Lett. 2010;31:260–2.

Jakub K, Pei-Lan H, Paul H, Peter WW, Craig LK, Mike S, et al. Epitaxial graphene transistors on SiC substrates. IEEE T Electron Dev. 2008;55:2078–85.

Wu YQ, Ye PD, Capano MA, Xuan Y, Sui Y, Qi M, et al. Top-gated graphene field-effect-transistors formed by decomposition of SiC. Appl Phys Lett. 2008;92:092102.

Melinda YH, Barbaros O, Yuanbo Z, Philip K. Energy band-gap engineering of graphene nanoribbons. Phys Rev Lett. 2007;98:206805.

Xiaolin L, Xinran W, Li Z, Sangwon L, Hongjie D. Chemically derived, ultrasmooth graphene nanoribbon semiconductors. Science. 2008;319:1229–32.

Obradovic B, Kotlyar R, Heinz F, Matagne P, Rakshit T, Giles MD, et al. Analysis of graphene nanoribbons as a channel material for field-effect transistors. Appl Phys Lett. 2006;88:142102.

Radisavljevic B, Radenovic A, Brivio J, Giacometti V, Kis A. Single-layer MoS2 transistors. Nat Nanotechnol. 2011;6:147–50.

Qiu H, Pan LJ, Yao ZN, Li JJ, Shi Y, Wang XR. Electrical characterization of back-gated bi-layer MoS2 field-effect transistors and the effect of ambient on their performances. Appl Phys Lett. 2012;100:123104.

Sunkook K, Aniruddha K, Wan-Sik H, Jong HL, Jiyoul L, Jaehyun Y, et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals. Nat Commun. 2012;3:1011.

Jiang P, Yohei Y, Keng-Ku L, Lain-Jong L, Yoshihiro I, Taishi T. Highly flexible MoS2 thin-film transistors with ion gel dielectrics. Nano Lett. 2012;12:4013–7.

Sung-Wook M, Hee SL, Hyoung JC, Min KP, Taewook N, Hyungjun K, et al. Nanosheet thickness-modulated MoS2 dielectric property evidenced by field-effect transistor performance. Nanoscale. 2013;5:548–51.

Dominik L, Andras K. Breakdown of high-performance monolayer MoS2 transistors. Acs Nano. 2012;6:10070–5.

Youngki Y, Kartik G, Sayeef S. How good can monolayer MoS2 transistors be? Nano lett. 2011;11:3768–73.

Liu H, Neal TA, Ye DP. Channel length scaling of MoS2 MOSFETs. Acs Nano. 2012;6:8563–9.

Junji S, Kazutoshi K, Shinsuke H, Ryoji K, Seiji S, Takaya S, et al. Excellent effects of hydrogen postoxidation annealing on inversion channel mobility of 4H-SiC MOSFET fabricated on (11 2 0) face. IEEE Electr Device Lett. 2002;23:13–5.

Se-Won L, Won-Ju C. Evaluation of the effects of thermal annealing temperature and high-k dielectrics on amorphous InGaZnO thin films by using pseudo-MOS transistors. J Korean Phys Soc. 2012;60:1317–21.

Mi RM, Sekwon N, Haseok J, Tae HL, Donggeun J, Hyoungsub K, et al. The effects of a combined thermal treatment of substrate heating and post‐annealing on the microstructure of InGaZnO films and the device performance of their thin film transistors. Surf Interface Anal. 2012;44:1431–5.

Joshi P, Romero HE, Neal AT, Toutam VK, Tadigadapa SA. Intrinsic doping and gate hysteresis in graphene field effect devices fabricated on SiO2 substrates. J Phys-Condens Mat. 2010;22:334214.

Zengguang C, Qiaoyu Z, Chenxuan W, Qiang L, Chen W, Ying F. Toward intrinsic graphene surfaces: a systematic study on thermal annealing and wet-chemical treatment of SiO2-supported graphene devices. Nano lett. 2011;11:767–71.

Pirkle A, Chan J, Venugopal A, Hinojos D, Magnuson CW, McDonnell S, et al. The effect of chemical residues on the physical and electrical properties of chemical vapor deposited graphene transferred to SiO2. Appl Phys Lett. 2011;99:122108.

Plechinger G, Schrettenbrunner F-X, Eroms J, Weiss D, Schüller C, Korn T. Low‐temperature photoluminescence of oxide‐covered single‐layer MoS2. Phys Status Solidi-R. 2012;6:126–8.

Saptarshi D, Hong-Yan C, Ashish VP, Joerg A. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 2012;13:100–5.

Weber T, Muijsers JC, Wolput JHMCV, Verhagen CPJ, Niemantsverdriet JW. Basic reaction steps in the sulfidation of crystalline MoO3 to MoS2, as studied by x-ray photoelectron and infrared emission spectroscopy. J Phys Chem. 1996;100:14144–50.

Peery AS, Mclntyre NS. A Raman and XPS investigation of supported molybdenum oxide thin films. 2. Reactions with hydrogen sulfide. J Phys Chem. 1993;97:11031–6.

Wang HW, Skeldon P, Thompson GE. Thermogravimetric-differential thermal analysis of the solid-state decomposition of ammonium tetrathiomolybdate during heating in argon. J Mater Sci. 1998;33:3079–83.

Bensimon Y, Belougne P, Deroide B, Ducourant B, Giuntini JC, Zanchetta JV. Influence of oxygen on electrical conductivity of amorphous molybdenum sulfides. J Non-cryst Solids. 1991;134:239–48.

Ni HZ, Wang MH, Luo QZ, Wang YY, Yu T, Wu HY, et al. The effect of vacuum annealing on graphene. J Raman Spectrosc. 2010;41:479–83.

Acknowledgements

This research was supported by the MSIP (Ministry of Science, ICT and Future Planning), Korea, under the ‘IT Consilience Creative Program’ (NIPA-2014-H0201-14-1002) supervised by the NIPA (National IT Industry Promotion Agency).

Author information

Authors and Affiliations

Corresponding author

Additional information

Competing interests

The authors declare that they have no competing interests.

Authors' contributions

SDN participated in the fabrication of the MoS2 field-effect transistor, measured the electrical properties of the transistor, analyzed the results, and wrote the manuscript. SY helped fabricate the channel, drain, source, and gate of the transistor and participated in the interpretation of the result. KP, AJC, HK, and JYK participated in the analysis of the result. All the authors proofread and approved the final manuscript.

Additional file

Additional file 1:

Supplementary figures. The file contains Supplementary Figures S1 to S3.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made.

The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

To view a copy of this licence, visit https://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Namgung, S.D., Yang, S., Park, K. et al. Influence of post-annealing on the off current of MoS2 field-effect transistors. Nanoscale Res Lett 10, 62 (2015). https://doi.org/10.1186/s11671-015-0773-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-015-0773-y